Motor speed control using a fault tolerance implementation on SRAM-based FPGA

DOI:

https://doi.org/10.57056/ajet.v8i2.137Keywords:

Microblaze Softcore, Three Modular redundancy, dependability, critical-safety applicationsAbstract

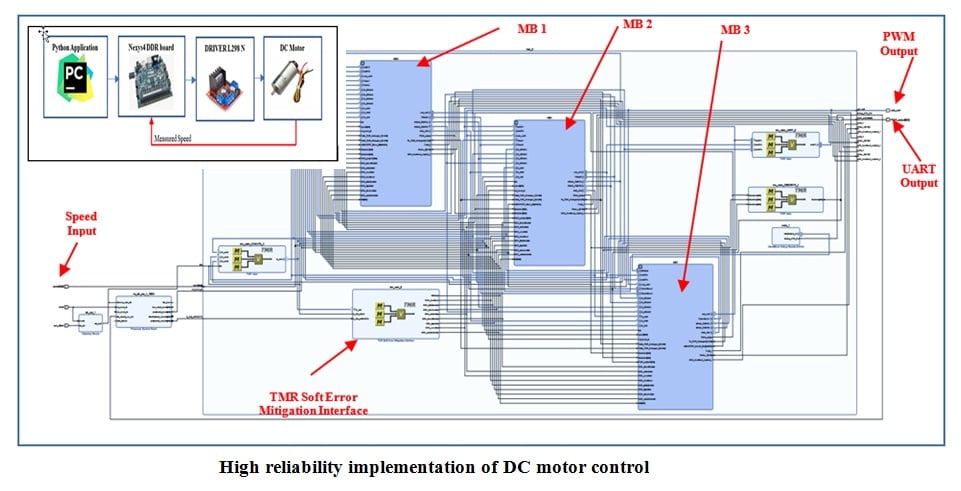

DC motor speed control is a critical task in many applications, such as industrial automation, aerospace and robotics. To ensure reliable and robust performance, a fault tolerance implementation is necessary. In this paper, we present a DC motor speed control system using an SRAM-based Field-Programmable Gate Array (FPGA) with a fault tolerance implementation. The control system utilizes a Pulse Width Modulation (PWM) and Proportional Integral Derivative (PID) to regulate the voltage applied to the motor. To ensure the reliability of the system, a MicroBlaze Triple Modular Redundancy is implemented, in which multiple controllers control the motor in parallel and their outputs are compared. The results show that the implementation significantly improves the reliability and robustness of the DC motor speed control system.

References

Joseph SB, Dada EG, Abidemi A, Oyewola DO, Khammas BM. Metaheuristic algorithms for PID controller parameters tuning: Review, approaches and open problems. Heliyon. 2022.

Kastensmidt F, Rech P. FPGAs and parallel architectures for aerospace applications. Soft Errors and Fault-Tolerant Design. 2016.

Bernardeschi C, Cassano L, Domenici A. SRAM-based FPGA systems for safety-critical applications: A survey on design standards and proposed methodologies. Journal of Computer Science and Technology. 2015;30:373-390.

Zhu ZK, Yuan Y, Zhang XH. Theodolite-camera videometrics system based on total station. InInternational Symposium on Photoelectronic Detection and Imaging 2011: Advances in Imaging Detectors and Applications 2011 Aug 18 (Vol. 8194, pp. 706-715). SPIE.

Agarwal C, Gupta A, Modeling, simulation-based DC motor speed control by implementing PID controller on FPGA. 2013.

Jain RV, Aware MV, Junghare AS. Implementation of a PID control PWM module on Altera DE0 kit using FPGA. In2016 IEEE First International Conference on Control, Measurement and Instrumentation (CMI) 2016 Jan 8 (pp. 341-345). IEEE.

Kangas N, A Comparison of High-Level Synthesis and Traditional RTL in Software and FPGA Design. 2020.

Wang J, Li M, Jiang W, Huang Y, Lin R. A design of FPGA-based neural network PID controller for motion control system. Sensors. 2022;22(3):889.

Fowler K. Mission-critical and safety-critical systems handbook: Design and development for embedded applications2009: Newnes.

Leroux P. Radiation tolerant electronics. Electronics. 2019;8(7):730.

Michael Henze MME. FPGAs enable development of safety-critical embedded systems. Safety & Security, 2018. EmbeddedWorld2018.

Kastensmidt FL, Carro L, da Luz Reis RA. Fault-tolerance techniques for SRAM-based FPGAs. Dordrecht: Springer; 2006.

Brosser F, Milh E. SEU mitigation techniques for advanced reprogrammable FPGA in space. Chalmers University of Technology, 2014.

Cao Y, Leroux P, Steyaert M. Radiation-tolerant Delta-sigma Time-to-digital Converters. Springer International Publishing; 2015.

León AF. Trends and patterns of ASIC and FPGA use in European space missions. 2013.

Carcheri JC. N-Modular Redundancy Techniques for Fault Tolerance in Reconfigurable Logic Devices. Master’s Project Report. 2015.

Kastensmidt, F. and R. Reis, Soft error rate and fault tolerance techniques for FPGAs, in Circuit Design for Reliability 2015, Springer. p. 207-221.

Yang M, Hua G, Feng Y, Gong J. Fault-tolerance techniques for spacecraft control computers. John Wiley & Sons; 2017.

Bridgford B, Carmichael C, Tseng CW. Single-event upset mitigation selection guide. Xilinx Application Note, XAPP987 (v1. 0). 2008:69.

Assurance SP. Techniques for Radiation Effects Mitigation in AASIC and FPGAs Handbook. Technical report, ESA Requirements and Standards Division; 2016.

Stoddard AG. Con guration Scrubbing Architectures for High-Reliability FPGA Systems. Brigham Young University; 2015.

Xilinx, MicroBlaze Triple Modular Redundancy (TMR) Subsystem v1.0. Product Guide, 2018.

Downloads

Published

How to Cite

Issue

Section

License

Copyright (c) 2023 El Habib Bensikaddour, Aissa Boutte

This work is licensed under a Creative Commons Attribution-NonCommercial 4.0 International License.